DE LA RECHERCHE À L'INDUSTRIE

# leti

**Annual Research Report 2014**

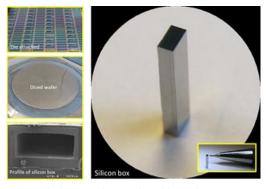

Silicon Technologies and Components

**Leti** is an institute of **CEA**, a French research-and-technology organization with activities in energy, IT, healthcare, defence and security.

By creating innovation and transferring it to industry, Leti is the bridge between basic research and production of micro- and nanotechnologies that improve the lives of people around the world.

Backed by its portfolio of 2,200 patents, Leti partners with large industrials, SMEs and startups to tailor advanced solutions that strengthen their competitive positions. It has launched more than 50 startups. Its 8,000m² of new-generation cleanroom space feature 200mm and 300mm wafer processing of micro and nano solutions for applications ranging from space to smart devices. Leti's staff of more than 1,700 includes 200 assignees from partner companies. Leti is based in Grenoble, France, and has offices in Silicon Valley, Calif., and Tokyo.

Visit www.leti.fr for more information

Within CEA-Leti, Silicon Technologies and Components research activities are shared between two divisions gathering together around 600 researchers.

**The Silicon Technologies Division** operates 24 hours a day, 7 days a week, all year round, 7,500m<sup>2</sup> of state-of-the-art cleanroom space divided into three different technological platforms.

**The Silicon Components Division** carries out research on nanoelectronics and heterogeneous integration on silicon and is focusing on two mains areas: on-going shrinking of CMOS devices to extend "Moore's Law" for faster, less-expensive computing power, and the integration of new capabilities into CMOS, such as sensors, power devices, imaging technology, and new types of memory, to enable new applications.

| Edito Simon Deleonibus<br>Chief Scientist, CEA Research Director | 4  |

|------------------------------------------------------------------|----|

| Edito Jean-René Lèquepeys<br>Head of Silicon Components Division | 6  |

| Edito Fabrice Geiger<br>Head of Silicon Technologies Division    | 8  |

| 2014 Key Figures                                                 | 11 |

| Silicon Divisions & Platforms                                    | 12 |

| Scientific Activity Indicators                                   | 14 |

| PhD Degrees Awarded in 2014                                      | 15 |

| Core & Beyond CMOS                                               | 23 |

| Memories                                                         | 31 |

| Patterning                                                       | 37 |

| Energy                                                           | 45 |

| Modeling & Simulation                                            | 51 |

| Passive & RF Components                                          | 57 |

| MEMS Actuators & Sensors<br>& Reliability                        | 63 |

| 3D Integration & Packaging                                       | 71 |

| Physical-Chemical Characterization & Metrology                   | 79 |

| Emerging Process                                                 | 89 |

#### **Dear Reader**

We are proud to release our fifth annual Silicon Components and Technologies Annual Scientific Research Report, for the year 2014. This booklet contains 56 one-page research summaries covering advances in the focus areas of our Silicon Divisions, highlighting new results which have achieved at least two publications during the year.

In 2014, the Silicon Divisions produced 413 publications, including 85 in peer-reviewed journals, achieving Impact Factors as high as 21. We published 435 grade-A items, which include peer-reviewed presentations at international technical conferences sponsored by scientific organizations, peer-reviewed journal papers, and internationally awarded patents.

I am particularly proud to highlight our 17 oral presentations at the 2014 International Electron Device Meeting (IEDM), held in San Francisco last December, which included four invited talks [1-4]. This is an exceptional accomplishment for the Silicon Divisions, placing CEA-Leti in the top tier of institutions worldwide at the major flagship conference on electron device research. It is even more exceptional because we demonstrated the maturity reached by FDSOI and its ability to foster future 2D and 3D applications, as well as the co-integration and achievements of More Moore and More than Moore devices.

More specifically, at nodes below 10nm, active device architecture will be strongly dependent on the control of channel electrostatics and geometric variability. In this dimensional range, we need to envision a reduction of intrinsic variability towards zero. To this end, 1D nanowires and atom-thick 2D materials are good candidates for co-integration in an augmented 3D Si-based Diversified CMOS platform [1].

Power consumption at the system level can be reduced to zero thanks to opportunities in materials engineering, device architecture, heterogeneous combinations of More Moore and More than Moore devices, and packaging [1,2]. Energy supply and storage can be implemented by incorporating adapted harvesters and thin-film batteries [1].

The heterogeneous co-integration of Nano-Electro-Mechanical Systems (NEMS) and CMOS enables high-resolution gas sensing with better figures of merit (signal-to-noise ratio, speed, power consumption) compared to standalone solutions [2]. Nanowire technology can be leveraged to achieve NEMS cantilever multi-gas sensor gauges.

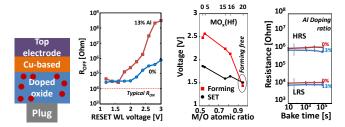

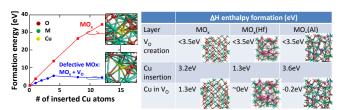

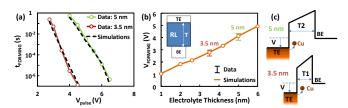

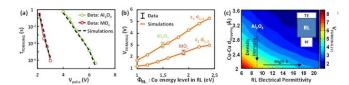

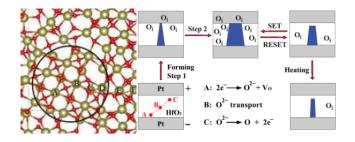

Memory hierarchy revision gives new opportunities to low-voltage switching embedded non-volatile resistive memories (RERAMs) [3]; these can be integrated with logic, for applications beyond data storage. Conductive Bridge RAMs and Ox-RAMs are good candidates for the applications [3]. They will enable drastic new architecture-based improvements in power consumption, latency and design through circuits with reconfigurable, programmable or neuromorphic architectures [3].

Communication with the outside world will be essential to future systems' autonomy and connectivity. SOI substrates, with high resistivity and trap options, have brought major advantages for optimization of front-end component integration, thanks to the reduction of parasitic losses in both passive and active devices, as well as superior isolation compared to bulk [4].

All these subjects have been among our top priorities since I defined the scientific direction of the Silicon Divisions. I am proud to see CEA-Leti keeping its leadership position with a clear vision of the advanced SOI roadmap for 2D&3D co-integration of More Moore and More than Moore devices.

In 2014, Silicon Components and Technologies Divisions members received 76 awards and distinctions – resounding recognition from their peers serving on high-level committees, at societies and with the technical programming groups of international conferences. In addition, our assignees and their co-workers received 12 awards and recognitions of personal distinction from their peers, at conferences and by selection committees. Our researchers won eight awards at international conferences. These honors were earned through strong collaborative teamwork and commitment, and our senior staff members were distinguished four times by their peers.

During the past nine years, I have been very happy to establish and oversee the scientific direction of the Silicon Components and Technologies Divisions (which included 1013 members at the end of 2014). We have created the necessary tools to manage scientific objectives, long-term roadmaps, the selection and review of thesis topics (some 35 new subjects per year and follow up of more than 140 PhD students), internships (about 50 new subjects each year) and post-doctoral research (15-20 new subjects annually).

The value of this activity can be measured through scientific performance, such as publications in highlighted conferences and peer-reviewed journals (a total of more than 400 per year on average), achievement of more than one grade-A publication per potential publishing researcher, exceptional funding such as ERC Grants (three awarded to the Silicon Divisions in the past five years), and international awards and recognitions from our peers. Because patents are vital to our partners' future success, our publication activity is complemented by intellectual property activity – 2014 saw 132 patents filed, 123 with international award.

The special position held by our Silicon Divisions requires committed support of our development activity and maintainance of top-quality research, while retaining strong connections to fundamental academic investigation. This commitment is illustrated by our fostering of long-term efforts through internal CEA Flagship programs, such as ZeroPOVA and A3DN. This continues a multi-decade Silicon Divisions tradition of offering state-of-the-art technology platforms to the scientific community, with the support of CEA.

Our visibility and international recognition are made possible by our international collaborations with major teams at Tokyo Institute of Technology, Caltech, Stanford University, the University of California, Berkeley; École Polytechnique Fédérale de Lausanne, and Albany-Nanotech; and by our participation in major international conferences through technical program committees, boards of governors, and evaluation committees. Underlying all these efforts is the cooperation of all our researchers and management, as well as the Silicon Division scientific committee that I had the pleasure and honor to establish and lead.

I wish great luck to my successors and greetings to the entire staff of the Silicon Components and Technologies Divisions. I also wish to extend my appreciation to the 10 chapter editors and authors of the 2014 Scientific Report, who spared no effort to make it a valuable reference document.

I advise my dear colleagues to keep in mind the popular saying: "Before the baobab grew up (several decameters span), the seed was there (several centimeters in size)." The Silicon Technologies and Components Divisions have demonstrated this principle in the past and have strong assets to continue demonstrating it into the future.

Grenoble, April 10, 2015,

Simon Deleonibus, Chief Scientist, CEA Research Director, IEEE Fellow

#### Invited papers at IEDM 2014, San Francisco, USA, Dec 15-17, 2014

[1] S. Deleonibus *et al.*, "Future Challenges and Opportunities for Heterogeneous Process Technology. Towards the Thin Films, Zero Intrinsic Variability Devices, Zero Power Era".

[2] J. Arcamone et al., "Nanosystems Monolithically Integrated with CMOS: Emerging Applications and Technologies".

[3] E. Vianello *et al.*, "Resistive Memories for Ultra-Low-Power Embedded Computing Design".

[4] C. Raynaud et al., "Technology Pathfinders for Low Cost and Highly Integrated RF Front End Modules".

#### **Dear Reader**

The global semiconductor industry achieved record sales of \$336 billion in 2014 - but will that trend continue in years to come? Today there are many significant uncertainties.

Our technological roadmaps are grappling with the potential end of Moore's law, the complexity of FinFET, FDSOI adoption, delays on 450mm and extreme UV lithography, and other challenges. Our collaborative models and alliances are faced with the multiplication of mergers, changing relationships between fabless companies and foundries, and the growth of the Chinese ecosystem. And future market development hinges on a wide range of factors, including the Internet of Things, Big Data, High Performance Computing and servers, and e-health.

In this evolving context, our division has reaffirmed its world-leading position in nanoelectronics research and, once again in 2014, delivered cutting-edge technology solutions to its industrial partners.

In particular, the work done by CEA-Leti on FDSOI has enabled STMicroelectronics to convince Samsung and GlobalFoundries of the industrial importance of this technology, which offers an excellent alternative to FinFET thanks to a positive trade-off between performance (speed, power consumption, etc.) and manufacturing cost. Meanwhile, we obtained important results on power electronics, which allowed us to establish new partnerships to advance our GaN-on-silicon technology and help create a global technology ecosystem. Finally, we successfully continued the globalization strategy of our MEMS activities. Today, Leti is widely seen as one of the world-leading laboratories in our field, and this greater visibility brings us new clients.

Without being exhaustive, I would like to highlight some major breakthroughs from 2014.

#### **CMOS**

- We demonstrated the dynamic performance of 14nm FDSOI devices, demonstrating their competitiveness with 14nm FinFET. Also last year, 28nm FDSOI achieved production maturity at Samsung Electronics Corp., stemming from a process codeveloped by Leti and STMicroelectronics.

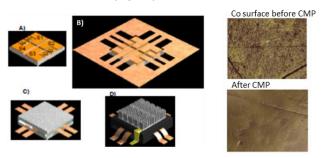

- We proved the implementation of our innovative CoolCube<sup>™</sup> concept on 300mm wafers in a production environment. CoolCube<sup>™</sup> aims at sequential fabrication of vertically stacked transistors and offers true benefits of going to the vertical dimension, because the stacked layers can be connected at the transistor scale. This new technology has attracted interest from Qualcomm and other companies, including IBM, ST and Altera.

- We recorded notable results on memories, including the first functional demonstrator of 12Mbit PCM memory incorporating Leti's phase-change material, and demonstration of more than 100 million cycles on a OxRAM memory built using STMicroelectronics' 28nm CMOS technology.

■ Finally, we realized the 3D assembly of two 65nm logic chips connected by an asynchronous network on chip (NoC) – a world first! This is the result of excellent collaboration, internally between our design and silicon divisions, and externally with partners ST and Mentor Graphics.

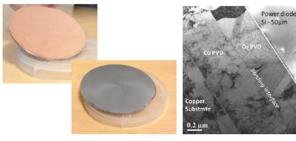

### **Power Electronics and Energy**

- Investments made in power electronics have started to bring positive results: realization of GaN power transistors on Si substrates with 30A current capability and 600V breakdown voltage, and strong patent activity (12 patents registered in 2014 on our innovative Normally-Off architectures).

- The start-up Exagan, created in April 2014, fulfills the desire to establish in France a real industrial ecosystem around GaN on silicon. The startup has a fab-lite model, keeping the technological capability to fabricate GaN wafers using GaN epitaxy on 200mm silicon, but outsourcing power component production to a foundry.

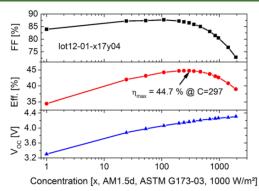

- In collaboration with Soitec and the Fraunhofer ISE, we achieved a new world record in the field of concentrated photovoltaics (CPV) with a conversion efficiency of 46.5% measured by the Fraunhofer (or 46% measured by the AIST).

- In the field of thin-film batteries, we supported STMicroelectronics' ramp-up of EnFilm™ technology.

#### **Microsystems**

- We demonstrated a "combo" sensor made of three accelerometers, three gyroscopes, and three magnetometers co-integrated on the same die.

- First images were obtained with an ultrasound probe made by VERMON that integrated our cMUT sensors.

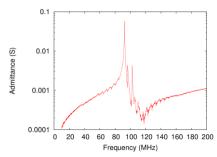

- We established a new state-of-the-art benchmark on BAW filters with Lithium Niobate resonators, which exhibit an exceptional electromechanical coupling coefficient (kt² = 59%). This opens the door to wide-bandwidth filters and new concepts of tunable acoustic filters.

- We supplied our spinoff start-up WAVELENS with a functional MEMS autofocus capability, and they obtained their first prototyping request from big players in the smartphone industry.

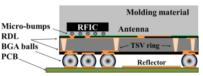

- We developed a new concept of 60GHz silicon-integrated antennas based on surface high-impedance (SHI) reflectors and realized through 3D integration. It combined high integration and performance.

All these results were obtained due to the sustained efforts of our team members, and I would like to sincerely thank all of them. Their excellent scientific work was recognized again in several papers at major conferences, including IEDM, VLSI, and Transducers. This report provides an overview of their many achievements.

Grenoble, April 13, 2015 Jean-René Lèquepeys, Head of Silicon Components Division

#### **Dear Reader**

The mission of our division is to provide our internal and external customers with the best innovative engineering solutions, so they can perform world-leading research on next-generation technology nodes. To achieve this, we need to provide the most advanced research facilities in the industry. Therefore, we are continuously investing in new buildings and new process tools.

In 2014, we realized 28.5M€ investment in new manufacturing equipment. This figure includes 4.3M€ dedicated to upgrading our installed base and streamlining our equipment portfolio. Tools put into production last year included latest-generation 300mm as well as online metrology and offline characterization equipment.

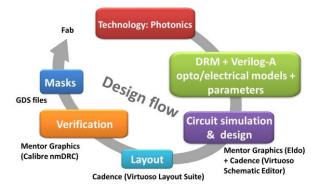

Our cleanroom upgrades are continuing; late last year we added 500m<sup>2</sup> to our 300mm line. Moreover, we have begun building a new cleanroom dedicated to photonic-on-silicon processes, with a completion date in 2017.

This internal investment is complemented by a strong policy of collaboration with tool manufacturers. The idea is to build win-win partnerships. CEA-Leti takes advantage of innovative tools or materials to develop next-generation technologies. In return, our partners gain insight into the requirements needed for future process nodes, enabling them to execute solutions well ahead of global semiconductor industry roadmaps. This resulted in the following achievements:

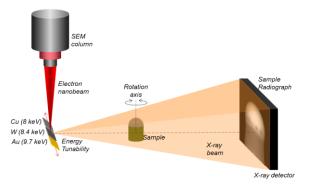

- We renewed three common labs: one with ASELTA Nanographics to jointly develop e-beam proximity effect correction solutions for both mask writing and maskless lithography (ML2) applications, another with Arkema to address development and industrialization of lithography based on nanostructured polymers, and a third with FEI to use holography and nanobeam diffraction techniques to characterize advanced semiconductor materials for the 22nm technology node and beyond.

- We strengthened and extended strategic partnerships with Applied Materials on the CoolCube<sup>TM</sup> transistor stacking concept, new-generation memories and advanced CMOS; with Lam Research on III-V materials etching; and with EVG to optimize temporary and permanent bonding technologies related to 3D TSV integration.

The year also was rich in scientific results for our division with a record number of more than 200 scientific papers produced and more than 40 patents filed. The international recognition we received (six distinctions and awards obtained in 2014) proves the excellence of our teams and their accumulated skills and expertise.

Our team is focusing on key challenges around advanced CMOS, 3D, photonics and advanced memories. We are also addressing key 200mm challenges around MEMS, power electronics, RF, magnetic materials, and other fields. Examples of our achievements include:

- A team comprised of CEA-Leti, Debiotech SA, the Swedish Royal Institute of Technology (KTH) and Mecaplast SA won a silver medal in the 2014 Medical Design Excellence Awards for a MEMS-based micro-needle that allows precise, pain-free injection of up to 0.5ml of vaccines and medications in a few seconds.

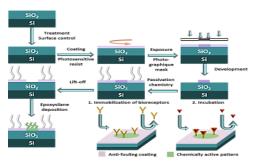

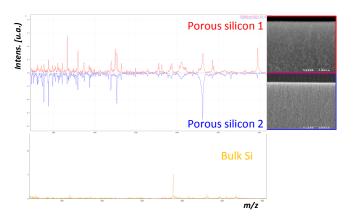

- Through common work with Clinatec Institute, we realized a new platform based on porous silicon, dedicated to versatile and efficient detection of biomarkers.

- We transferred know-how to Toyota on the characterization of dopants in SiC devices.

- We developed a new 300mm CMP process for 3D integration of imagers.

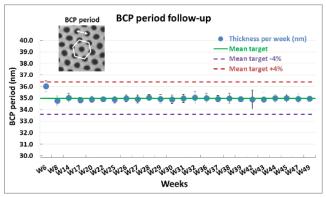

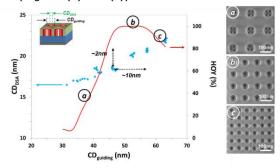

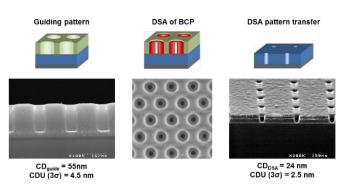

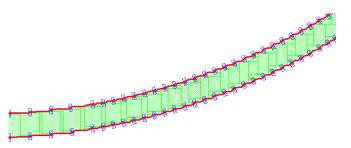

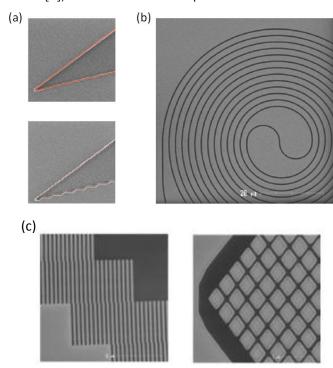

- We developed a new directed self-assembly (DSA) process. It can, independent of guide density, properly direct alignment, thus relaxing the resolution requirements of the lithography process.

- We advanced an innovative TEM characterization technique with a sample holder that allows in-situ and in-operando use at atomic scale on semiconductor devices.

- We incubated a start-up focused on ultra-sensitive and ultra-fast Raman spectroscopy, to overcome the limitations of existing analysis techniques (speed, cost, bulky equipment, etc.).

This scientific annual report includes additional details about all these key achievements, which were made possible by the work of our researchers and technicians. I would like to take this opportunity to thank all of them for their constant commitment.

Grenoble, April 14, 2015

Fabrice Geiger, Head of Silicon Technologies Division

607 Permanent Staff 222 Industrial Residents 147 PhD Students 37 Post-Docs

200 & 300mm Platforms for CMOS and MEMS

7,500 m<sup>2</sup> Clean Rooms

500 Process Tools

Continuous Operation

132 Patents Filed in 2014 413 Scientific Papers Produced in 2014

16 Common Laboratories 1 Startup Company Created in 2014

**The silicon divisions** operate 7,500m2 of state-of-the-art cleanroom space divided into three platforms, gathering 500 process tools and a combined staff of more than 450; they run industry-like operations, 24 hours a day, 7 days a week, all year round.

- The Nanotech200&300 platform provides 200mm and 300mm CMOS wafer processing, which can be applied to both semiconductor and microsystem devices.

- The MEMS200 platform produces non-CMOS Micro-ElectroMechanical Systems (MEMS).

Both platforms are focused on the More than Moore initiative to develop new semiconductor capabilities. An innovative cleanroom shuttle system now links the two platforms to add process flexibility and faster processing.

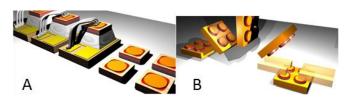

- The third platform 3D Integration aims to integrate various microelectronics objects together in order to juxtapose complementary functions (such as sensing, storing, processing, actuation, communication and energy scavenging) hence providing advanced system solutions in 3 dimensions. This line is open to our customers for prototyping through the Open3D service.

- All research carried out in our cleanrooms benefits from the Nano-Characterization Platform, which is located on the MINATEC campus. This platform, unique in Europe, covers 8 domains of competencies, including electron microscopy, X-ray diffraction, Ion Beam analysis, optics, magnetic resonance, scanning probe, surface analysis and sample preparation.

#### **Silicon Technologies division** is organized according six departments.

- Three Process Departments: their missions are to realize generic process steps for all projects and to develop innovative processes to provide state-of-the-art solutions to internal and external customers. Those departments are focused on patterning, deposition, and surface treatments. Their research activities in collaboration with key universities allow LETI's advanced position in the future.

- A Characterization Department: its mission is to perform off-line observations to characterize process steps, materials or components. This department also has a research activity to maintain its level of excellence.

- Two Support Departments: one is in charge of the planning, the interface with internal divisions or external customers as well as methods, training and clean-concepts. The other is responsible for facilities operations and engineering.

**Silicon Components Division** is organized around three departments with clear objectives and market focus.

- MOS Department mission is to simulate, model, develop, demonstrate and test new generations of circuits and modules for sub-20nm CMOS, digital and memory.

- MEMS Department mission is to design and develop innovative microsystem components (sensors, actuators and RF) and associated toolbox (packaging, heterogeneous integration, reliability).

- Power and Energy Department is to develop and demonstrate technology modules and components for power and energy (photovoltaic, power electronics, integrated storage).

#### **Publications**

In 2014: 413 publications produced

Ratio "A grade published items/ Publishing researchers" = 1.00 (including grade A conferences, journals and international extended patents)

#### **Distinctions and Awards**

12 distinctions and awards obtained in 2014

- Best Student/Young Scientist Award MRS Spring Meeting 2014 (San Francisco), Manuela Aoukar et al.

- Bronze Medal, 2014 Junior Scientist and Industry Annual Meeting (Grenoble), Larissa Djomeni et al.

- Outstanding Student Paper Award, 2014 ECS Fall Meeting (Cancun), Paul Gondcharton et al.

- Outstanding Student Paper Award, 2014 ECS Fall Meeting (Cancun), Damien Massy et al.

- Best Paper Award, EPTC2014 (Singapore), Sebastien Mermoz et al.

- Young Scientist Award 2014, EMRS (Lille), Viktoria Gorbenko et al.

- 1<sup>st</sup> Prize Art & Sciences Contest, 2014 Int. Conf. On Electron Microscopy (Krakow), Cyril Guedj et al.

- Best Student Paper Award, IMAPS 2014 (San Diego), David Laloum et al.

- Simon Deleonibus, Visiting Professor at Tokyo Institute of Technology, Japan.

- Simon Deleonibus, Chair IEEE Electron Device Society, Region 8 (Europe-Russia, Africa, Middle East).

- Simon Deleonibus, IEEE Transactions on Electron Device, 6 Years Editor Award.

- Simon Deleonibus, IEEE Electron Device Society Board of Governors, 6 Years Elected Member Award.

76 added Awards among which 2005 Grand Prix Académie des Technologies, 2008 IEEE Cledo Brunetti Award, 2011 French-German Prize for Economy, 2011 Silver Medal ST Microelectronics, 2012 SEE Grand Prix du Général Ferrié, 3 ERC Grants, 48 Best Papers Awards.

#### **Expertise and Recognitions**

97 CEA experts: 4 Research Director, 7 International Experts

25 Researchers with habilitation qualification "HDR" (to independently supervise doctoral candidates).

1 IEEE Fellow, 3 IEEE Seniors

#### **Scientific Committees**

3 Journal Editors: IEEE TED, European Physical Journal-Applied Physics, Science China-Information Sciences.

7 researchers involved in ITRS (International Technology Roadmap for Semiconductors)

40 members of Technical Programs and Steering Committees in major conferences:

IEDM, VLSI Technology Symposium, IRPS, ESSDERC, SSDM, ECTC, ECS...

Awards committees: IEEE Cledo Brunetti Award, IEEE Paul Rappaport Award, SEE & IEEE Brillouin-Glavieux Award, European Research Council Panel

Boards of Governors: IEEE ED Society, Nanosciences Foundation Board, IEEE CPMT, SFV IEEE ED Society Region 8 Vice-Chair

#### **International Collaborations**

Collaborations with more than 50 universities and institutes worldwide

Tokyo Institute of Technology, CALTECH, University of Stanford, University of Berkeley, University of Cambridge, University of Tokyo, EPFL, Albany-NT, ...

### PhD Degrees Awarded in 2014

**Bilel SAIDI**University of Toulouse

### Metal Gate Work Function Modulation Mechanisms for 20-14nm CMOS Low Thermal Budget Integration

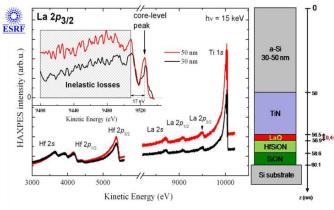

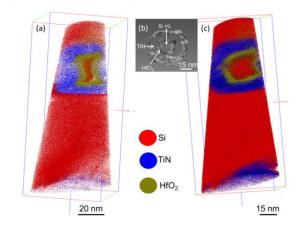

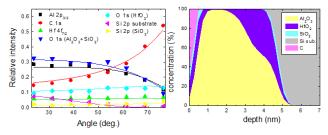

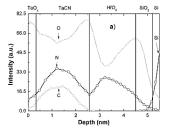

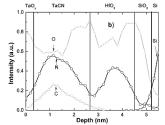

Since the 45nm CMOS technological node, the microelectronics industry replaced the historical SiO<sub>2</sub>/polysilicon gate stack by the high permittivity oxide (HK)/metal gate (MG) couple. If this choice solved the problem of undesired leakage currents, other difficulties appeared due to the uncontrolled interdiffusion and reactivities of the new gate materials. This is the consequence of the high thermal budget required for the CMOS integrated in the gate first fabrication process. To minimize these difficulties, one option consisted in implementing a new integration scheme with a lower thermal budget like the so-called "gate last" process. In the frame of this approach, gate materials are needed today for the sub-20nm complementary MOS (CMOS) technological nodes in particular for low-power mobile applications (smart phone, ebook). To fit the International Technology Roadmap for Semiconductors requirements, gate materials deposited on HfO2 (the chosen high permittivity oxide that replaced SiO<sub>2</sub> in microelectronics since 2007) with sub-nm equivalent oxide thickness (EOT) control and effective work function (EWF) relevant for nMOS and pMOS co-integration (CMOS) are required. TiN was already a well-known pMOS compatible metal electrode for HfO2. Finding CMOS compatible gate materials with an n-type character was more challenging. For this, we investigated layers of reactive materials deposited on TiN. Single metals like Ti and Al and the binary metallic system TiAl were considered. Then, the case of the ternary TiAlN metal alloy directly deposited on HfO<sub>2</sub> with different N content was examined. We particularly focused our effort on understanding the origins of the electrical parameters (EWF and EOT) variations measured after a low thermal budget process (T≤400°C). A systematic investigation of the elemental distributions across the stack and of the chemical environments was performed by physico-chemical methods (spatially resolved STEM EDX/EELS, TOF-SIMS and back-side XPS) in addition to thermodynamic considerations. By this way, we determined the particular behavior of N and O with respect to Ti, Al and the binary TiAl and their impact on the electrical parameters. The chemical species interdiffusion, in particular their distribution at HK/MG interface, is correlated to the electrodes EWF modulation. Besides, the EOT variation is related to the remote oxygen scavenging from the SiO<sub>2</sub> interfacial layer that is always present between the Si substrate and the HK. This phenomenon induced by the AI, Ti or TiAI metals has been understood on the basis of an advanced thermodynamic study of these materials behavior with respect to oxygen including their free energy of oxide formation and oxygen solubility. Results obtained were helpful to understand the more complex case of the ternary TiAIN metal alloy directly deposited on HfO<sub>2</sub>. By simply varying the N content, this electrode defines the best compromise for a variable EWF compatible for both nMOS and pMOS with a sub-nm EOT. The thermal stability of these electrodes is shown to be limited to temperatures going from 500°C to 700°C depending on the stack considered (TiN/AI, TiN/TiAl or TiAlN). Innovate was another aspect of our work. Therefore, we proposed alternative gate materials. Ta and Ni were studied with different configurations and alloyed with different metals on HfO2 (TaN/Ta, Ta/Ni, Ni/Ti). Here again, the thermodynamic behavior with respect to oxygen and nitrogen and the thermal stability of these innovative electrodes is evaluated to understand their different performances compared to HfO<sub>2</sub>/TiN(Al)-based gate stacks. In particular, Ni/Ti alloying is shown to be very promising for a CMOS co-integration at low thermal budget (T≤600°C) in gate last approach.

Assawer SOUSSOU

University of Grenoble

### Modeling and Characterization of Electrical Effects of Ge Integration in Metal/High-k/SiGe MOS Structures

Maintaining good threshold voltage (VT) centering is a paramount challenge for CMOS technology. The SiGe introduction in bulk and FDSOI pFETs requires VT control for such devices. To this end, we have to extract accurately electrical parameters and to understand Ge integration effects in SiGe based pFETs. In this thesis, first, we have proposed extraction methods to determine VT, at band voltage (VFB) and equivalent oxide thickness (EOT) parameters in bulk and FDSOI transistors. The extraction methods have been validated via Poisson-Schrodinger (PS) simulations and successfully applied to measurements. Second, we have highlighted and explained electric effects of Ge on pMOS gate stack parameters. Electrical characterizations compared with PS simulations have evidenced an additional effective work function increase, induced by Ge, related to interfacial dipoles. STEM, EELS and SIMS characterizations have demonstrated that dipoles are located at SiGe/IL interface.

Yohann SOLARO

University of Grenoble

### Conception, Realization and Characterization of Innovative ESD Devices for FDSOI Technologies (28nm and 14nm Nodes)

Electrostatic Discharges (ESD) are a recurrent problematic faced by the microelectronic industry, compromising the reliability of integrated circuits. Moreover, dimensions shrinking of the transistors, caused by the pursuit of performance enhancements of the CMOS circuits make ESD protection design more and more difficult. FDSOI architecture (Fully Depleted Silicon On Insulator) allows a significant improvement of the electrostatic behavior of the MOSFETs transistors for the advanced technologies. It is industrially employed from the 28nm node. However, the implementation of ESD protections in these technologies is still a challenge. While the standard approach relies on SOI substrate hybridization (by etching the BOX (buried oxide)), allowing to fabricate vertical power devices, we focus here on structures where the current flows laterally, in the silicon film. In this work, several solution of the literature are first reviewed. Alternative approaches are proposed for the 28nm and 14nm FDSOI technologies. They use innovative "band modulation" devices (Z2-FET and BBC-T). Their static, quasi-static and transient characteristics are studied, with TCAD simulations and electrical characterizations. Different optimizations are studied, from the technology and the design point of view, allowing improving the low and high current characteristics of these new protection elements. In particular, the influences of parameters such as the geometry, biasing conditions, thicknesses, or doping levels are analyzed in detail.

### Heimanu NIEBOJEWSKI University of Lille

#### Self-Aligned Contacts for the 10nm FDSOI CMOS Technology

For sub-14nm transistor generations, the integration of classical metallic contacts subjected to optical lithography limitations prevents the fulfillment of alignment performance required by design rules (64nm gate pitch for the 10nm node) and industrial yields.

In the frame of this PhD. work, an original transistor architecture featuring self-aligned contacts (SAC) is studied for CMOS FDSOI technologies.

First, a Self-Aligned Contacts (SAC) module has been integrated and validated on a CMOS 14nm FDSOI process flow. The feasibility of SAC integration at a more aggressive gate pitch (10nm node) has also been demonstrated morphologically. The impact of such integration on the transistor and circuit performance, in terms of parasitic capacitances especially, has been evaluated through numerical simulations (TCAD, SPICE) in the case of the 10nm FDSOI technology. Finally, several techniques inducing mechanical stress within the transistor channel have been analyzed in order to improve the device performance. Among those, the use of contacts on source-drain to induce such stress has been particularly investigated.

### Thomas CABOUT

### Technological Optimization and Electrical Characterization of Oxide Based Resistive Memories (OxRRAM) for Low Power Applications

Today, non-volatile memory market is dominated by charge storage based technologies. However, this technology reaches his scaling limits and solutions to continue miniaturization meet important technological blocks. Thus, to continue scaling for advanced nodes, new non-volatile solutions are developed. Among them, oxide based resistive memories (OxRRAM) are intensively studied. Based on resistance switching of Metal/Isolator/Metal stack, this technology shows promising performances and scaling perspective but isn't mature and still suffer from a lake of switching mechanism physical understanding.

Results presented in this thesis aim to contribute to the development of OxRRAM technology. In a first part, an analysis of different materials constituting RRAM allow us to compare unipolar and bipolar switching modes and select the bipolar one that benefit from lower programming voltage and better performances. Then identified memory stack TiN\HfO<sub>2</sub>\Ti have been integrated in 1T1R structure in order to evaluate performances and limitation of this structure. Operating of 1T1R structure have been carefully studied and good endurance and retention performances are demonstrated. Finally, in the last part, thermal activation of switching characteristics have been studied in order to provide some understanding of the underling physical mechanisms. Reset operation is found to be triggered by local temperature while retention performances are dependent of Set temperature.

### Raphaël LACHAUME University of Grenoble

### Contribution to the Electrical Characterization and to the Numerical Simulation of the Silicon Heterojunction Solar Cells

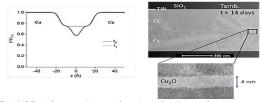

By combining the advantages of thin-films and crystalline silicon (c-Si), the silicon heterojunction solar cell technology (HET) achieves a better cost-performance compromise than the technology based only on c-Si. The aim of this thesis is to improve the understanding of the physical mechanisms which govern the performance of these cells by taking advantage of specific characterization and simulation skills taken from microelectronics. Our study focuses on the front-stack of the n type cell composed of thin layers of indium tin oxide (ITO) and hydrogenated amorphous silicon (a-Si:H). We begin with a theoretical and experimental study of the conductivity of a-Si:H layers as a function of temperature, doping concentration and bulk defects density. It is important to properly take into account the dopant/defect equilibrium of these layers but we also show that the work function of the electrodes in contact, such as the ITO, can strongly influence the Fermi level in the nano-films of a-Si:H. Then, we evaluate seven characterization techniques dedicated to the work function extraction in order to identify the most suitable one for studying degenerate semiconductors such as the ITO. We particularly show the interest of using original microelectronics techniques such as capacitance C(V), leakage current I(V) and internal photoemission (IPE) measurements on ITO/bevel oxide/silicon test structures. We clearly demonstrate that the ITO bulk properties can be optimized, yet the interfaces have a major influence on the extracted values of the effective work function (EWF). A good overall consistency has been obtained for C(V), I(V) and IPE measurements on a silicon dioxide bevel (SiO2) ; the extracted values enabled us to explain experimental results concerning the optimization of HET cells. We show that the open circuit voltage (Voc) of these devices is finally barely sensitive to work function, unlike the Fill Factor (FF). This is due to the a-Si:H layer. The more it is doped, defective and thick, the more it is able to screen the electrostatic variations of EWF. Thus, EWF must be sufficiently high to be able to reduce the p a-Si:H layer thickness and, in turn, to gain in short-circuit current (Jsc) without losing either in FF or Voc. Finally, we successfully applied this methodology to other types of transparent conductive oxides (TCO) differing from ITO. The best candidate to replace ITO must not only have a high optical transparency, be a good conductor and have a high EWF, but we must also pay close attention to the possible interface degradations caused by the deposition techniques.

### Benoît SKLENARD University of Grenoble

### Physical Modeling of Junction Processing in FDSOI Devices for 20 nm Node and Below

Complementary metal oxide semiconductor (CMOS) device scaling involves many technological challenges in terms of junction formation, in particular for 3D sequential integration and Fully Depleted Silicon on Insulator (FDSOI) architectures. In this thesis, the physical phenomena involved during the junction formation at a low processing temperature (i.e.  $\leq 600^{\circ}$ C) have been studied. Such a process relies on Solid Phase Epitaxial Regrowth (SPER) of an amorphous region to activate the dopants. A new model based on Kinetic Monte Carlo (KMC) method has been developed in order to simulate SPER at the atomistic scale. This model has been used to understand the regrowth anisotropy and provide an explanation for the formation of defects as well as to get insight into the influence of a non-hydrostatic stress and the presence of electrically active dopants on the regrowth kinetics.

### **Daniele SETTE**University of Grenoble

### Functional Printing: From the Study of Printed Layers to the Prototyping of Flexible Devices

In the last decade, functional printing has gained a large interest for the manufacturing of electronic components. It stands aside to silicon technologies and specifically targets markets of large area devices (screens, photovoltaics) and flexible electronics (RFID antennas, sensors, smart textiles). In this work, inkjet printed silver layers are characterized depending on the printing conditions and the required post-printing annealing. The evolution of their microstructure, electrical and mechanical properties is investigated as a function of the annealing temperature. The correlation of the measurements with theoretical models supports the experimental methods that were developed. The knowledge of the printed silver layers assets and the optimization of the printing process lead to the design, fabrication and characterization of flexible electronics devices: a 17GHz band-pass filter

the design, fabrication and characterization of flexible electronics devices: a 17GHz band-pass filter printed on polyimide, a flexible vacuum micro-sensor working on the Pirani principle, and a 250µm thick membrane switch for keyboards. Finally, all-printed RF capacitors were realized by stacking Barium Strontium Titanate (dielectric) and silver printed layers. These prototypes exhibit performances near the state-of-the-art and suggest new opportunities for printing technologies. This thesis offers a thorough study of inkjet printed silver layers and assess their potential for the manufacturing of flexible devices.

### Julie ABERGEL University of Grenoble

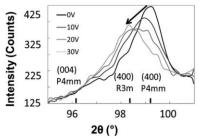

#### **High-Strain Piezoelectric Materials for MEMS Actuation**

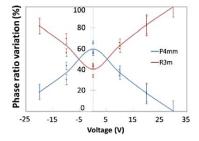

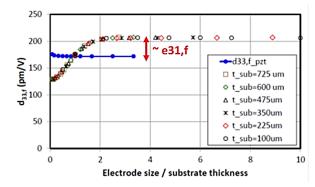

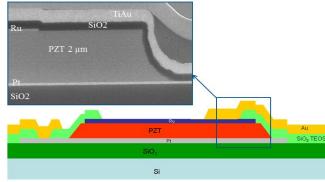

Piezoelectric actuators exhibit low response times and high deflection/actuation voltage ratios. This PhD thesis aims at optimizing their strain values by increasing the applied field and the piezoelectric coefficients. To target low voltage issues, Aluminum Nitride (AIN) ultrathin layers were deposited and characterized. e31,eff coefficient was found to be constant between 800 and 50nm, at a value as high as -0.8C/m<sup>2</sup>. Piezoelectric behavior was also shown for 12nm-thick AIN layers, by three different ways. Still in order to apply high electric fields, a study was carried out to improve Lead Zirconate Titanate (PZT) breakdown field, by inserting lanthanum atoms. Breakdown field was improved by approximately 35%, with no decrease of permittivity or piezoelectric coefficients. Another optimization approach consists in increasing the material's piezoelectric coefficients. In this view, PZT was characterized around several phase transitions. Near morphotropic phase boundary, piezoelectric effect was found to be enhanced: e31,eff coefficient raises up to -18 C/m<sup>2</sup> at low field conditions and -27C/m² in actuating conditions. Domain wall pining issue was also discussed. Near Curie transition, dielectric properties were found to be enhanced, with a dielectric constant rising up to 2640 at 370C, which is almost twice as high as room temperature value. Furthermore, dielectric loss decreases from 25C to 280C to reach 1.6%. To profit from a critic phase transition, highly Lanthanum doped PZT was deposited. Relaxor behavior was shown and an induced piezoelectric coefficient d31 of -25 pm/V was measured. Materials developed in this PhD thesis can be used to realize microactuators and especially inkjet print-heads.

### Remy DEJAEGER University of Lyon

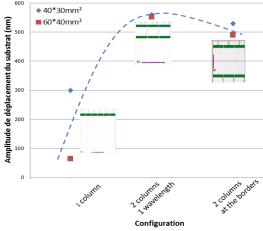

### Multi-Physic Modelization, Realization and Characterization of a Piezoelectric MEMS Digital Loudspeaker Array

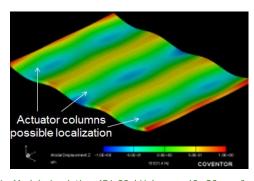

The Digital Loudspeaker Array (DLA) is an electroacoustic transducer which receives as input a digital signal and performs the analog conversion directly into the air. It consists of a plurality of radiating elements arranged in a matrix. These elements will be designated by the term « speaklet » when they are reduced in size. The acoustic radiation of a DLA is indeed very sensitive to the size of the matrix due to differences in path length, which makes it especially suitable for MEMS technology. This thesis presents study of a piezoelectric MEMS DLA. After an introduction that is increasingly focused on the subject, the thesis addresses the multiphysics modeling of the DLA, dimensioning of the speaklets and experimental tests.

Analytical formulas, numerical simulations and finite element models are developed and used to predict the mechanical behavior of the presented speaklets, the pressure radiated by the DLA and the electrical power consumption. The speaklets are then dimensioned from the technological stack (set in advance) in order to maximize the pressure level. Experimental tests involving the use of an anechoic chamber, an optical interferometer, a vibrometer and an impedance-meter validate most of the models. Otherwise, these tests are useful for improving some of them or for showing their limitations. The results have shown the importance of the residual stresses, which cause an initial deformation of the speaklets and modify their Eigen frequencies, thus rendering ineffective the use of large radii. In accordance with the models, the static deflection of the speaklets is nonlinear but their dynamic behavior is linear. This enables characterizations using transfer functions. Theory and sound recordings show that a DLA made of such speaklets can produce in the best case the same pressure as the one generated by the same matrix driven in an analog way. In our case, more distortions were obtained in digital reconstructions because of non-uniform responses of the speaklets, due to different access resistances. However, the presented DLA has other advantages, the most important being the very low power consumption it is theoretically possible to achieve using the adiabatic charge principle. The piezoelectric MEMS DLA thus appears as a promising technology. The optimization of our first prototype using the developed tools should indeed lead to a DLA able to generate a pressure equivalent to the one obtained with analog control, but with a far greater electroacoustic transduction efficiency. Future work should then focus on the design of nonlinear speaklets and on the shaping of the pulse of pressure they generate, in order to increase the total pressure level.

### Fabrice CASSET University of Lille

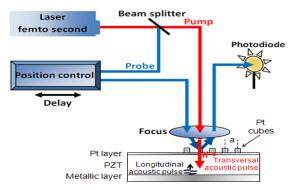

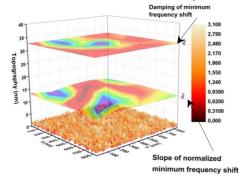

### Mechanical Properties Characterization of Thin-Film PZT for MEMS Applications using Picosecond Ultrasonics

MEMS components are today an economic reality and are already used in many mass market applications. These devices can use a piezoelectric actuation, in particular based on thin-film PZT due to its high piezoelectric coefficient. To perform predictive design of high performances components based on PZT actuators, mechanical properties of the PZT are required. We used the picosecond ultrasonic technique which probes thin layers with high frequency acoustics waves generated by ultrashort laser pulses. It allows the transposition of the sonar principle at nanometric scale. During this PhD, we studied thin-film PZT using picosecond ultrasonics. We extracted both Young's modulus and Poisson ratio without an approximation of one or the other. We also studied wall domain relaxation using picosecond ultrasonic measurement at various frequencies. Using PZT mechanical properties obtained from picosecond ultrasonics, we extracted the PZT piezoelectric coefficient, from the comparison between PZT-based cantilever measurement and numerical modeling. Finally, we applied these data for the design of haptic plates using thin-film PZT actuators. The good agreement between haptic plate measurements and modelization proves all the benefit of picosecond ultrasonics for MEMS design.

### Paul IVALDI University of Grenoble

#### AIN based Cantilever Resonator for Gravimetric Gas Sensors

With the development of micro and nano technologies in the last three decades, the performances of gas chemo sensors have been improved drastically, paving the way for new applications. Especially, these new devices with provided low fabrication cost, high sensitivity and miniature size are very good candidates for applications where high performances are required and heavy, expensive and slow instruments such as such GC and MS are not viable technically or economically. This is the case, in particular, for on-field detection of warfare agents, monitoring of indoor air pollution and medical diagnosis. The main objective of this PhD thesis is to investigate the piezoelectric transduction at the nano-scale for the development of high-resolution resonant micro-cantilever based gas sensor. To that mean, we have intended to cover the whole prototyping chain from the development of 50nm thick Aluminum Nitride (AIN) piezoelectric films with good piezoelectric properties to the gas sensing proof of principle experiment using cantilevers resonators actuated and detected piezoelectrically by the mean of these 50nm thick AIN films. We also have covered the theoretical analysis for sensing performance optimization of these devices and their read-out and control electronic circuits.

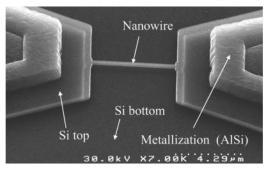

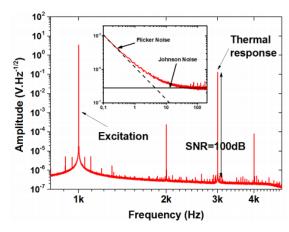

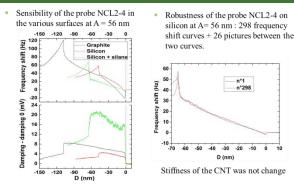

### Julien PHILIPPE University of Grenoble

### Technology of Fabrication and Work's Analysis of a Nanowires Sensor Co-Integrated CMOS for Medical or Environmental Applications

The Micro Electro Mechanical Systems (MEMS) devices are present everywhere in our daily life, since they are the main component of sensors present in many objects: our cars (airbag, pressure sensors) and our smartphones (microphones, accelerometers) for example. Their sub-µm downscaling has allowed the emergence of a new kind of devices called NEMS (for Nano Electro Mechanical Systems) and the possible use of these systems in specific applications in which a high level of sensitivity and resolution is necessary, such as gas sensing, mass spectrometry and molecules recognition using traditionally bulky machines. This thesis proposes a new way to fabricate mass detectors by implementing both NEMS devices and electronic circuit on the same chip in order to get a compact and high performance sensor for such application.

### Monica Larissa DJOMENI WELEGUELA University of Strasbourg

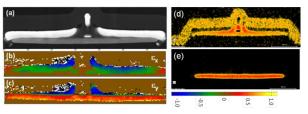

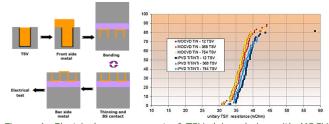

### Study of Through Silicon Via Integration Realized Through MOCVD for 3D Stacking of Microelectronic Components

For the past years, Moore's law has pointed mainstream microelectronics, driving integrated circuits down to 22 nm and below. Yet, performance, dimension and cost issues make it difficult to follow the trend. Integrating analog functions into CMOS-based technologies enables cost-optimized systems solutions. These diversified tendencies are known as "More than Moore". One of the key technologies of this trend is the TSV, which maintains the contact between two components.

The increasing aspect ratio of via made it critical to obtain a continuous, conformal coverage of the copper diffusion barrier layer using iPVD.

In the first part of this thesis, a promising deposition technique by MOCVD has been developed at low temperature to fulfill various integration schemes including via last and via middle processes.

Characterizations of the behavior of these materials in the TSV then became a great challenge in order to handle the integration protocol. Working at theses scales makes standard methods limited to evaluate the intrinsic properties inside the TSV. In the second part, the implementations of advanced characterization into these structures were carried out.

### Papa Momar SOUARE University of Saint-Etienne

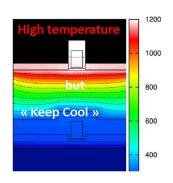

### Thermal Effects in 3D Stacks of Electronic Chip: Numerical and Experimental Studies

Today we are witnessing an evolution of mobile electronic systems to more advanced features. The complexity of mobile electronic systems requires an increase in computing power, which can be achieved either by the use of more aggressive CMOS technology ("Moore's law"), or by a technique called 3D integration ("More than Moore"). Three dimensional (3D) stack of electronic chips generates an increase of the power density dissipated per unit area. This power, essentially resulting from Joule effect in transistors and interconnections, contributes to increase the overall temperature of the stack. The global objective of this thesis is to study the heat transfer in a 3D stack of chips during operation. We will focus on understanding the geometric and materials effects of the stack and the impact of the placement of 3D interconnects (TSV, Bumps ...) on these heat exchanges. The study relies on both numerical simulations and experimental measurements on 3D stacks that validate the numerical model. These numerical and experimental studies can also be used to establish thermal design rules, especially for 3D interconnects placement and design. The establishment of such a thermal model is based on finite element simulations of an industrial 3D process in CMOS 65nm node. This allows an unprecedented accuracy in our thermal model. Indeed, previous simulations used compact models less accurate than finite elements - and a generic method that does not reflect all of the properties of materials and in particular interfaces. In the experimental part, accurate thermal mapping of the 3D stack are obtained using a large number of sensors embedded in the silicon, and under different conditions of 3D chip process. This provides a numerical model validated and calibrated by experimental measurements.

### Julien BERTHEAU University of Grenoble

### Study and Characterization of Intermetallics Interconnections based on Copper Pillars and SnAgCu Alloys for 3D Integration

Technological roadmap of the microelectronic industry is mainly described by Moore's law which aims a constant reduction of transistors size. Three-dimensional integration of active chips appears more and more as an alternative way to Moore's law. According to this strategy, chips are interconnected along the vertical axis thanks to copper pillars and a tin based alloy (SnAgCu). The joining is then performed through eutectic bonding using a SnAgCu solder alloy which is at the origin of intermetallic compounds growing at the copper alloy interface. These intermetallic compounds are sometimes described in literature as weakening factor of the interconnection mechanical reliability. Moreover this interfacial reactivity leads also to the formation of Kirkendall microvoids potentially causing interconnections breakings, mostly noticed during ageing tests.

This report is dedicated to the study and metallurgical characterization of the interconnection system with a size close to that of the actual prototypes which is 25µm. The study is successively focused on SnAgCu alloy microstructure, Cu/SnAgCu and Ni/SnAgCu interfacial reactivity and on the mechanical reliability of interconnection system. These topics are investigated in function of thermal constraints and during different integration steps until chips packaging. The main critical aspect is related to the fact that system dimensions, already small, are planned to be reduced, leading to a more important proportion of the solder alloy consumed by interfacial reaction.

### **Hélène ISSELE**University of Grenoble

### Characterization and Modeling of Mechanical Properties of Thin Films for the Manufacture of Microelectronic Devices - Application to the Field of 3D Integration

The fabrication of microelectronic devices using 3D integration technologies requires a good knowledge of mechanical issues. Indeed, the thin films that are integrated have various thermomechanical properties and are deposited onto a substrate that is thinned in order to carry out the interconnections. The level of stresses and strains in devices has to be strictly controlled during their processing.

The goal of this work is to exploit the characterization techniques available at the CEA-Leti and to couple them with modeling tools to address this issue. This coupling is used to control the mechanical behavior of a complex stack at each step of its fabrication. The experimental techniques that are used are non-destructive. The modeling tools take into account the elastic and thermal properties of each material involved in the stack, and also the intrinsic strains caused by the deposition of each layer. Coupled methodologies have been carried out to evaluate these input data. From a material database, a tool to predict the mechanical behavior of a multilayer stack was developed and validated experimentally. It enables to predict the level of strain and stress of the stack.

Mechanical predictions enable to guide the selection of materials in order to improve the devices integrity and optimize their fabrication. Reliability issues that occur in the long term, due to a significant level of stress and strain can also be anticipated.

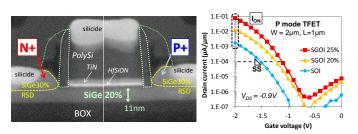

### Anthony VILLALON University of Grenoble

### Steep Slope Nano-Transistors for Ultra Low Power Applications

Band to band tunneling field effect transistor (TFET) is a PIN-gated architecture able to reach sub 60mV/dec subthreshold slopes at room temperature, which is an advantage over MOSFET in low power applications. The objective of this thesis is to study and characterize TFETs fabricated in CEA-Leti using MOSFET SOI technology. The first generation of devices is realized on planar FDSOI technology, and studies the impact of source/channel heterojunction, channel thickness and annealing temperature on device performances. The second generation is planar SiGe nanowire architecture, with research focusing on the impact of the wire geometry. Through measurements we were able to prove the band to band tunneling injection, while the reported performances were compared with literature and with MOSFET. Furthermore, advanced characterizations led to a better understanding of the output characteristics. Through low temperature measurements we confirmed existence of defects close to the junctions (which cause slope degradation), as well as on which process steps to improve in the future.

### Fabien PIALLAT University of Grenoble

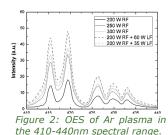

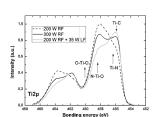

### Plasma Assisted Chemical Deposition (CVD/ALD) and Integration of Ti(Al)N and Ta(Al)N for sub-20 nm Metal Gate

Conformity requirements for the sub-20 nm technological nodes metal are beyond the possibilities of the currently used PVD deposition technique. CVD techniques, more specifically MOCVD and ALD, are identified as the best techniques for metal deposition. For metal-gate application, titanium and tantalum carbo-nitrides alloys are considered as the most promising. In this work, a detailed review of MOCVD and ALD deposition mechanisms and plasma influence on the deposited material is carried out. First, process windows for successful tuning of the metal properties are examined. Plasma impact on the metal and the inherent reaction mechanisms are also highlighted with the help of plasma characterization. Then great importance is given to the integration of these metals, by careful study of the interactions taking place at the interfaces. Correlations between physico-chemical properties and electrical behavior of the metal/high-k dielectric stack are introduced thanks to XPS characterization. Finally, aluminum doping of MOCVD TaN is considered for n-mos and p-mos gate characteristics achievement. By comparison of the properties and behaviors of Al doped metals deposited by PVD and MOCVD, diffusion mechanisms are proposed to explain the role of Al in the observed changes.

### **Damien RADISSON** University of Grenoble

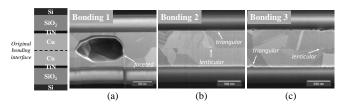

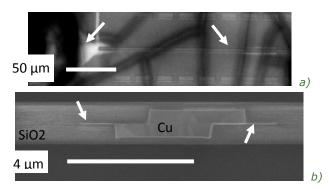

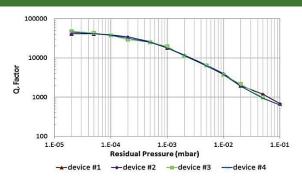

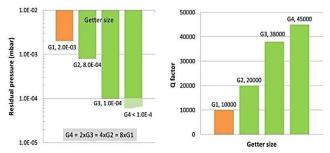

#### **Direct Bonding of Patterned Surfaces**

Direct bonding is a process by which two sufficiently flat and clean surfaces can bond to each other without any added adhesive layer. Direct bonding of patterned surfaces is often used for the fabrication of Micro-Electro-Mechanical Systems (MEMS), where a silicon wafer with cavities is bonded to a plain wafer. The fabrication of these devices is expensive and it would be useful to have quidelines when designing knew devices to know in advance if direct bonding will be possible.

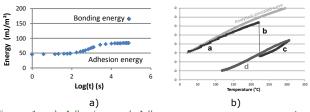

A 2D simulation model of the direct bonding of two substrates is developed and used to study the influence of the cavities on the bonding wave velocity. The prediction of the simulation run with Comsol® are in good coherence with the experimental measures and a 2D law of the bonding velocity is obtained. The bonding of perfectly flat wafers with cavities should always be possible. Limitations to the bonding of real wafers are due to the elastic energy cost of deforming the non-perfectly flat wafers. This limit is reached easily when the bonding wave must cross a trench, so a design with a small bonding guide to help cross the cavity will work best. The width of this wave guide should be chosen by considering the bow of the wafer. Indeed the second important design rule is to keep a bonding area big enough to have more adhesion energy than the elastic energy cost due to non-flat wafers deformation. The adhesion energy is an important parameter of the direct bonding, as it is the energy that drives the adhesion. This adhesion energy is different from the more widely known bonding energy which is the energy needed to separate two previously bonded wafers. In this work a simple method to measure the adhesion is proposed. Long time measurement of the evolution of the adhesion energy lead us to propose a mechanism for its evolution linked to the formation of capillary bridges between rough surfaces.

### Caroline RAUER University of Grenoble

### Silicon and Silicon Dioxide Direct Bonding : Understanding of the Involved Mechanisms

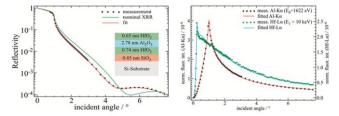

Direct wafer bonding refers to a process by which two mirror-polished wafers are put into contact and held together at room temperature by adhesive force, without any additional material. This technology feasible at an industrial scale generates wide interest for the realization of stacked structures for microelectronics or microtechnologies. In this context, a precise understanding of bonding mechanisms is necessary. Consequently, the aim of this work is to study the bonding mechanisms for hydrophobic silicon reconstructed surfaces and hydrophilic deposited silicon oxides surfaces.

In this study, bonding of hydrophobic silicon reconstructed surfaces and bonding of hydrophilic deposited silicon oxides prepared either by plasma activation or chemical-mechanical polishing were analyzed, as a function of post-bonding annealing temperature. For this, several characterization techniques have been used: bonding energy measurement, acoustic microscopy in order to observe defectivity, infrared spectroscopy and X-Ray reflectivity. Thus the bonding interface closure has been analyzed from a chemical and mechanical point of view and bonding mechanisms have been proposed for the studied bonded structures. Finally the study of deposited silicon oxide bonding prepared either by plasma activation or by chemical-mechanical polishing has led to some recommendations for efficient and high quality deposited silicon oxides bonding.

FDSOI: Advanced Modules and Design

Reliability and Variability Methods for Nano Transistors & Basic Circuit Elements

CoolCube<sup>™</sup> Integration

Very Low Temperature Deposition - Etch of SiGe:B Raised Sources and Drains for CoolCube<sup>TM</sup>

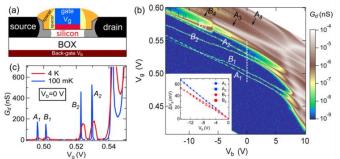

Tunnel Transistors (TFET) & Single Electron Transistors (SET) in Nanowire Architecture on SOI

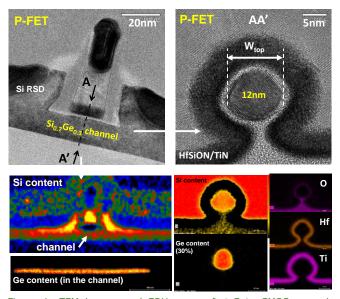

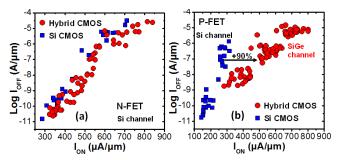

Advanced Nanowire FET Technology

### FDSOI: Advanced Modules and Design

#### Research topics: CMOS, SOI, FDSOI

B. De Salvo, J. Mazurier, O. Weber, O. Thomas

Partnership: IBM, STMicroelectronics, IMEP-LACH, SOITEC, Berkeley Wireless Research Center Sponsorship: Catrene-Dynamic ULP, Catrene-Reaching 22, ENIAC-Places2Be, Eurotalent

Planar FDSOI is an important device architecture for continued CMOS scaling [1-4] and an attractive alternative to more complex FinFET architectures. Its advantages include: excellent short channel electrostatics, un-doped channels, effective back bias for performance boost and leakage lowering; a more conventional, lower cost process.

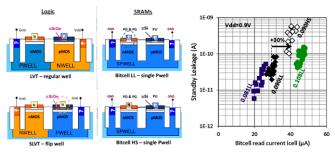

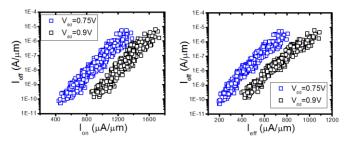

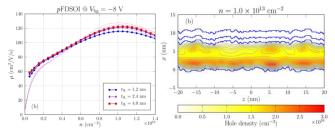

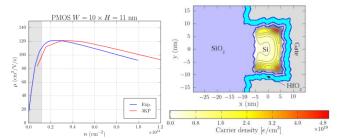

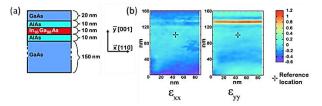

In [1], we presented a 14nm FDSOI technology designed for high speed and energy efficient applications using strainengineered FDSOI transistors (i.e. dual SOI/strained SiGeOI N/P channels). Compared to the 28nm FDSOI technology, this 14nm FDSOI technology provides 0.55x area scaling and delivers a 30% speed boost at the same power, or a 55% power reduction at the same speed, due to an increase in drive current and low gate-to-drain capacitance. Using forward back bias (FBB) we experimentally demonstrated that the power efficiency of this technology provides an additional 40% dynamic power reduction for ring oscillators working at the same speed. Finally, a full single-port SRAM offering was reported, including an 0.081µm<sup>2</sup> high-density bitcell and two 0.090µm² bitcell flavors used to address high performance and low leakage-low Vmin requirements.

In view of the 10nm node, we reported in [2] FDSOI devices with a 20nm gate length and 5nm spacer, featuring a 1.3 GPa tensile strained Silicon-on-Insulator (sSOI) channel NFET and 35%Ge partially compressive strained SiGe-on-Insulator (SGOI) channel PFET. At Vdd of 0.75V, competitive effective current (Ieff) reaches 550/340 µA/µm for NFET, at Ioff of 100/1 nA/µm, respectively. With a fully strained 30% SGOI channel on thin BOX (20nm) substrate and Vdd of 0.75V, PFET Ieff reaches 495/260 µA/µm, at Ioff of 100/1nA/μm, respectively. Competitive sub-threshold slope and DIBL are reported. With the demonstrated advanced strain techniques and short channel performance, FDSOI devices can be extended for both high performance and low power applications to the 10nm node. Moreover, a multimodeling (based on mechanical simulations, Noneequilibrium Green's functions simulations, piezoresistance coefficients, mobility analytical modeling, compact modeling) calibrated on state-of-the-art FDSOI devices was also developed [3]. It has been shown that high-mobility gains can be achieved for both NMOS and PMOS (sSOI substrate providing the major NMOS gain (x2); PMOS mobility being improved by a factor 8 both by the Ge fractions increase in channel/RSD and layout optimization (slicing), thanks to the high impact of uniaxial strain). Finally, FDSOI Ring Oscillator simulations showed that a dynamic power gain of 50% could be achieved while maintaining circuit frequency performance, thanks to strain

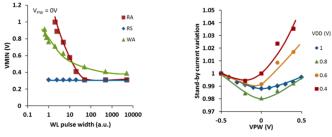

In [4], we demonstrated the 28nm ultra-thin body and buried oxide (UTBB) FD-SOI high-density (0.120µm²) single p-well (SPW) bitcell architecture for the design of low-power wide voltage range systems enabled by back-bias

adjustment. The results from a 140kb programmable dynamic SRAM characterization test module have provided both information about location and cause of failures as well as power and performance by mimicking system operating conditions over a wide supply voltage range. A 410mV minimum operating voltage and less than 310mV data voltage with less than 100fA/bitcell were retention measured. Improved bitcell read access time and writeability through back-bias were demonstrated with less than 5% of stand-by power overhead.

Figure 1: (left) Schematics highlighting logic & SRAM devices construction for multi VT and back bias optimization. (right) Icell vs ISB at Vdd=0.9V for 14FDSOI single port SRAM bitcells (after [1]).

Figure 2: sSOI NFET (left) Ion and (right) Ieff at Vdd of 0.9V and 0.75V (after [21).

Figure 3: RS, WA, RA VMIN vs WL pulse width (left) and I<sub>OFF</sub> vs VPW.

#### Related Publications:

- [1] O.Weber et al., "14-nm FDSOI Platform Technology for High-Speed and Energy-Efficient Applications", VLSI Techn. Symposium '14.

- [2] Q.Liu et al., "FDSOI CMOS Devices Featuring Dual Strained Channel and Thin BOX Extendable to the 10nm Node", IEDM 2014.

- [3] B. De Salvo et al., "A mobility Enhancement Strategy for sub-14nm Power-Efficient FDSOI Technologies", *IEDM* 2014. [4] O. Thomas et al., " Dynamic Single-P-Well SRAM Bitcell Characterization with Back-Bias Adjustment for Optimized Wide-Voltage-Range SRAM Operation in 28nm UTBB FD-SOI", IEDM 2014.

# Reliability and Variability Methods for Nano Transistors & Basic Circuit Elements

#### Research topics: FDSOI, Reliability, Dynamic Variability

X. Garros, A. Subirats, J. El Husseini, G. Reimbold

### Partnership: STMicroelectronics, IMEP-LAHC Sponsorship: ENIAC-Places2Be, LabEx-MINOS

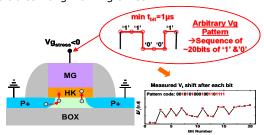

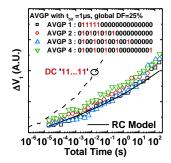

Negative Bias Temperature Instability (NBTI) is a key reliability concern which affects the working of digital & analog circuits. To address NBTI issue at circuit level, one standard approach is based on the modeling of the NBTI degradation measured at transistor level stressed under simple AC mode, i.e. an alternate sequence of '1' & '0' bits. Nevertheless, the real stress seen by the device in a circuit is not as regular as in this AC stress. We therefore propose a new fast characterization technique (~1µs range) able to measure the NBTI degradation under arbitrary gate stress patterns (see Fig.1). The stress sequence consists this time in an arbitrary succession of bits '1' or '0' corresponding to 2 gate bias values. This sequence of ~20 bits, called pattern, can be repeated up to 1E12 times. This method allows us demonstrating that the NBTI aging of a device integrated in a circuit mainly depends on the circuit activity and on its working frequency and not on the bits arrangement. An effective modeling was also provided to reproduce accurately the NBTI degradation (solid lines). This model can be integrated in a spice simulator to predict the degradation of a circuit after long working times.

Figure 1: AVGP method to measure NBTI aging under circuit working condition.

Figure 2: Vt shift induced by NBTI for different AVGPs.

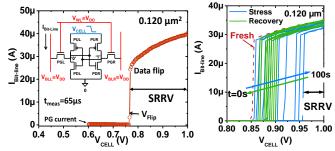

NBTI also induces a temporal variability of threshold voltage Vt in nano-scaled transistors which affects the stability and reliability of a SRAM cell. A new methodology based on the "Supply Read Retention Voltage" (SRRV) metric was

therefore proposed to address this concern in high density SRAM cells made in 28nm FDSOI technology. This technique shown in Fig.3 consists in measuring the read margin of the cell, through a direct measure of the bitline current. The method is equivalent to the butterfly method but it is faster. With this original method it is possible to measure how a BTI stress at strong Vdd impacts the read stability of the cell (see Fig.3 right).

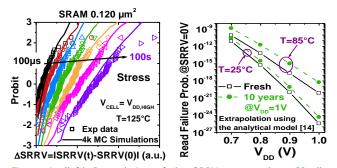

Figure 3: SRRV measurement (left) and its evolution with stress.

Moreover the degradation varies from one cell to another. That is why we are talking about "dynamic variability". This also explains why a statistical analysis must be used to address this issue. Experimental results are shown in Fig.4 and are well modeled by Monte Carlo SPICE simulations. This validates our simulation approach to evaluate the impact of the BTI stress on the PASS/FAIL of a complete SRAM matrix. The key result is that, in standard working conditions of the SRAM cut (VDD=1 V et T<85°C), the impact of BTI on the read stability of the 28nm FDSOI array is very small, even after 10 years working. This methodology based on measurements at the bitcell level is very useful for a complete evaluation of the reliability of large SRAM arrays. In the future, it will be applied to the study of the most advanced technology nodes.

Figure 4: (left) Degradation of the SRRV measured on 60cells at various stress times (right) Read failure probability of 100k SRAM array before & after a 10 years stress at Vdd=1V.

#### Related Publications:

[1] A. Subirats, X. Garros, J. Cluzel, J. El Husseini, F. Cacho, X. Federspiel, V. Huard, M. Rafik, G. Reimbold, G. Ghibaudo, "A new gate pattern measurement technique for evaluating the BTI degradation in circuit conditions", *IEEE Int. Reliability Physics Symp. (IRPS)*, 2014. [2] J. El Husseini, X. Garros, A. Subirats, A. Makosiej, O. Weber, O. Thomas, V. Huard, X. Federspiel G. Reimbold, "Direct measurement of the dynamic variability of 0.120µm2 SRAM cells in 28nm FD-SOI technology", *IEEE Symposium on VLSI Technology*, 2014.

[3] J. El Husseini, X. Garros, J. Cluzel, A. Subirats, A. Makosiej, O. Weber, O. Thomas, V. Huard, X. Federspiel and G. Reimbold, " A complete characterization and modeling of the BTI-induced dynamic variability of SRAM arrays in 28 nm FD-SOI technology", *IEEE Transactions on Electron Devices*, Vol. 61, No. 12, December 2014.

### **CoolCube™ Integration**

#### Research topics: 3D Sequential Integration, Low Thermal Processes

C. Fenouillet-Beranger, P. Batude, B. Mathieu, O. Turkyilmaz

Partnership: STMicroelectronics, IBM, Qualcomm, LASSE Sponsorship: Nano2017

Compared with TSV-based 3D ICs, CoolCube  $^{\text{TM}}$  or sequential 3D ICs presents "true" benefits of going to the vertical dimension as the stacked layers can be connected at the transistor scale.

CoolCube $^{\text{TM}}$  aims at processing transistors on top of each other sequentially. Its implementation faces the challenge of being able to obtain a high performance top transistor processed at sufficiently Low Temperature (LT) in order to preserve bottom FET performance.

This year several key points have been evaluated such as:

- Determination of maximum thermal budget supported by the bottom FDSOI transistor.

- Evaluation of nanosecond laser anneal as an alternative to SPER (Solid Phase Epitaxy Regrowth) for top transistor dopant activation.

- -Technological modules development such as low temperature gate stack, low-k spacer...

- Quantification of Power, Performance, Area (PPA) gain with CoolCube<sup>™</sup> integration versus planar technology for FPGA applications.

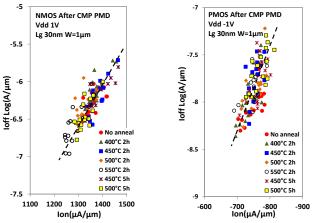

Determination of maximum thermal budget has been evaluated for advanced FDSOI technology with in-situ doped RSD (SiGe:B/ SiC:P) and SiGe channel for pMOS [1].

Various anneals have been applied after the pre-metal dielectric CMP ranging from 400°C up to 550°C, 2hours. Fig.1 shows that the transistor's performance is preserved whatever the thermal budget.

Figure 1: Determination of the maximum TB for bottom FET performance preservation. The Ion /Ioff trade-off is not degraded whatever the TB applied (up to 550°C, 2h).

Electrical analysis revealed no EOT regrowth no work function variation no junction modification. Despite a salicide

sheet resistance modification beyond 500°C, the NiPtSi salicide (NiPt with 15% Pt salicidation) presents no evidence of agglomeration. As a conclusion this technology can endure relatively high thermal budget (up to 500°C), opening new options for top FET fabrication.

One of the most critical thermal budgets in the top FET process is the dopant activation. Laser ( $\lambda$ =308nm, pulse 200ns) activation seems well adapted to 3D sequential as it enables a local annealing of the top MOSFET up to 1200°C while the temperature of the bottom one stays cool (500°C, corresponding to the temperature limit determined previously).

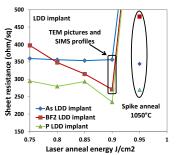

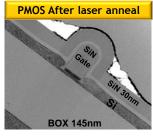

Fig.2 shows that successful RSD recrystallization has been obtained thanks to nanosecond laser anneal without melting the gate thanks to an appropriate capping. Also sheet resistance measurements shows that laser activation can largely compete with spike 1050°C anneal.

Figure 2: (left) Sheet resistance measurements for As, BF2, P versus laser anneal energy. RTA spike sheet resistance is also plotted as reference. (right) TEM cross section of a PMOS FDSOI transistor after RSD recrystallization using nanosecond laser anneal.

Finally PPA analysis on FPGA with stacked 14 nm-node-FETs shows an area reduction of 55% and Energy Delay product of 47% compared to the 14 nm node planar FDSOI integration [3]. Thus, CoolCube™ technology appears as an efficient way to pursue Moore's law in term of area and performance without resorting to transistor's scaling.

#### Related Publications:

[1] C. Fenouillet-Beranger, B. Mathieu, B. Previtali, M-P. Samson, N. Rambal, V. Benevent," New insights on bottom layer thermal stability and laser annealing promises for high performance 3D VLSI", *IEDM* 2014.

[2] P. Batude, M. Vinet, B. Previtali, C. Tabone, C. Xu, J. Mazurier et al., "Advances, Challenges and Opportunities in 3D CMOS Sequential Integration", IEDM 2011.

[3] O. Turkyilmaz, G. Cibrario, O. Rozeau, P. Batude, F. Clermidy, "3D FPGA using High-Density Interconnect Monolithic Integration", Design, Automation and Test in Europe Conference and Exhibition (DATE), 24-28 March 2014, Dresden, Germany.

# Very Low Temperature Deposition - Etch of SiGe:B Raised Sources and Drains for CoolCube<sup>™</sup>

#### Research topics: SOI, Monolithic 3D Integration, CMOS

J.M. Hartmann, V. Benevent, J.P. Barnes, M. Veillerot

### Partnership: STMicroelectronics, Probions Sponsorship: Nano2017

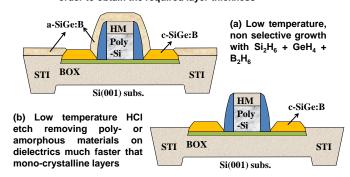

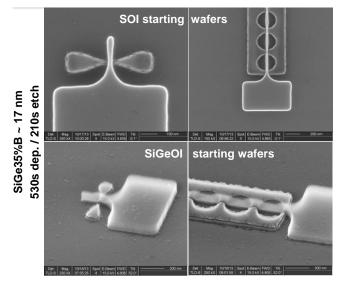

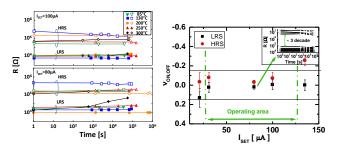

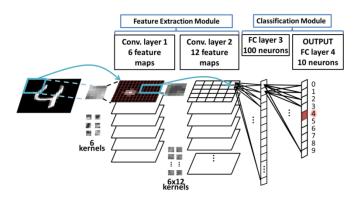

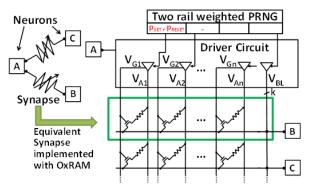

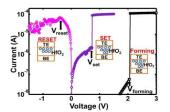

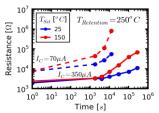

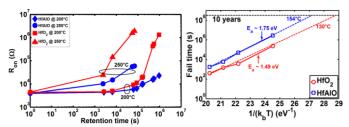

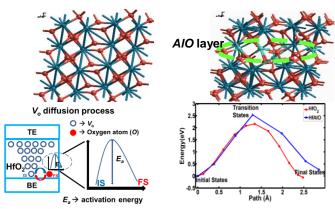

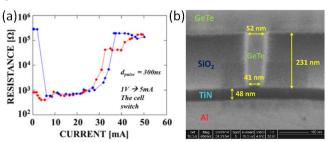

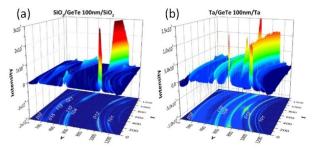

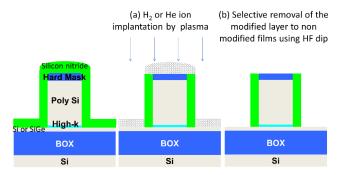

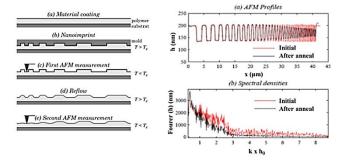

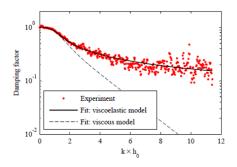

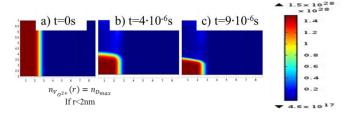

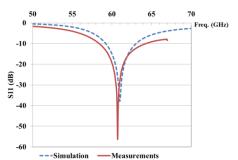

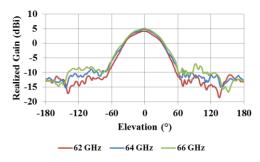

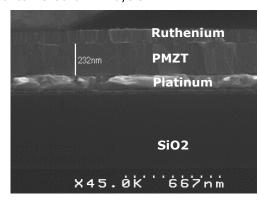

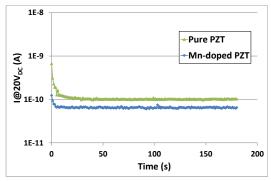

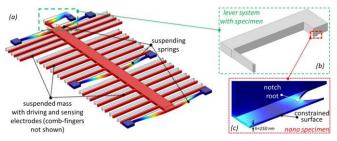

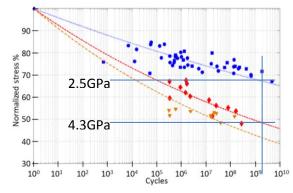

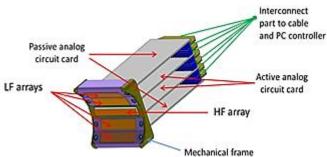

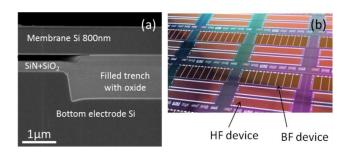

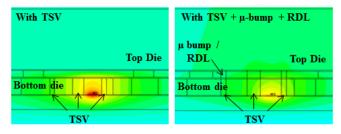

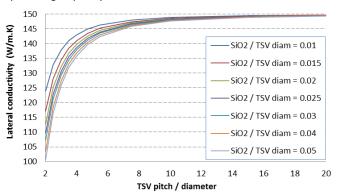

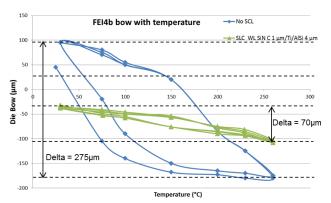

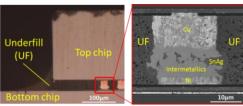

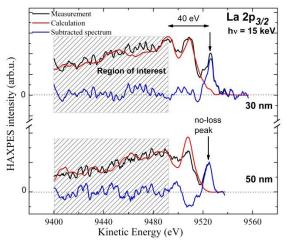

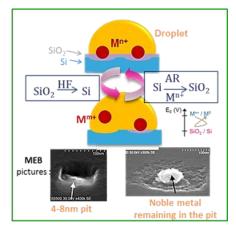

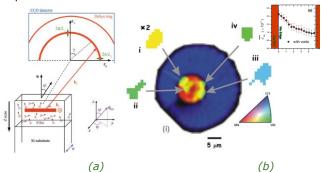

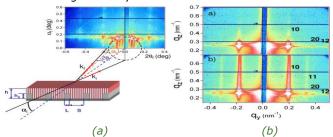

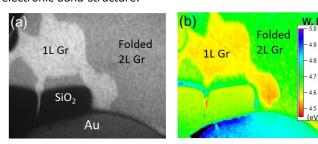

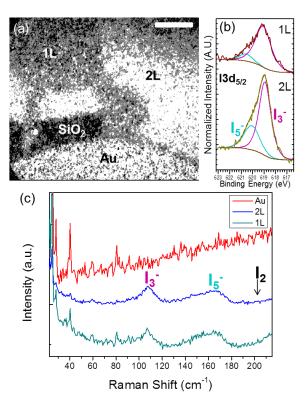

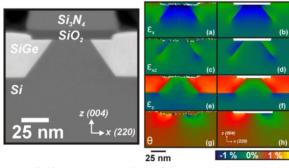

In-situ boron-doped SiGe Raised Sources and Drains (RSDs) are mandatory to thicken the access regions and lower the contact resistance of high performance p-type Metal Oxyde Semiconductor Field Effect Transistors (p-MOSFETs) built on top of Extra-Thin Silicon-On-Insulator (ET-SOI) substrates. They can also be handy in order to boost the ON current of Tunnel FETs on ET-SOI, improve the electrical performances of Omega-gate SOI Nano-Wire FETs etc. Such RSDs are typically 15-20 nm thick, with a Ge content close to 30% and a boron atomic concentration slightly higher than 1020 cm $^{-3}$ . They are usually grown at 650°C, 20Torr with a heavily chlorinated chemistry (i.e. with SiH<sub>2</sub>Cl<sub>2</sub> + GeH<sub>4</sub> + B<sub>2</sub>H<sub>6</sub> + HCl) in order to be fully selective versus SiO<sub>2</sub> (the isolation) and Si<sub>3</sub>N<sub>4</sub> (the transistor's spacers) [1].